希望各位高手帮忙指点迷津啊,呵呵非常感谢!

问题是: 要实现本地服务——存储器访问,根据波形应用的具体需求,为波形组件提供统一的存储器访问服务。 一个Master接口独占多块存储器(比如2个,一个是SDRAM,一个是DDR SDRAM),这里认为这些存储器均可由本地FPGA直接访问。

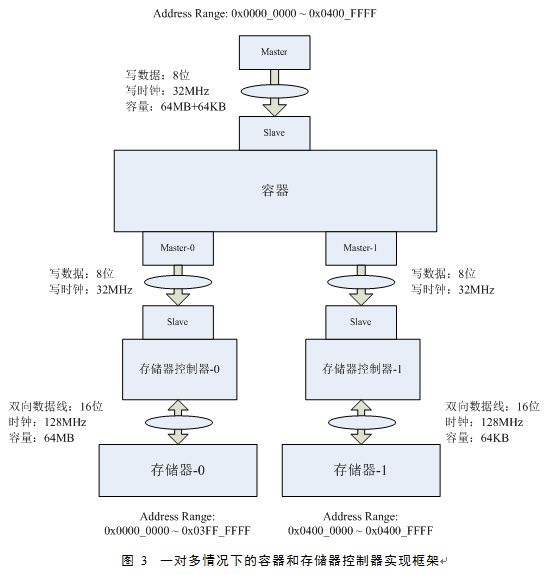

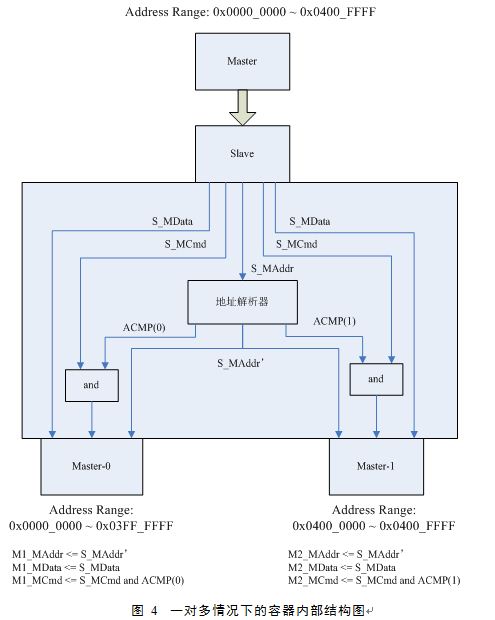

大概结构是这样的:组件和容器之间通过Maste 和slave连接,容器和存储器控制器之间也是通过Maste 和slave连接。 现在需要做的是①在容器中实现一个地址解析器来判断存取SDRAM还是DDR SDRAM; ②在存储器控制器中使用2个异步FIFO来适配存储器控制器和容器之间的时钟数据宽度差异。 最终需要的是用VHDL语言实现(要求接口符合OCP规范)。没看明白的看下图:

上图是从组件到容器到存储器控制器到存储器的整体结构,下图是容器内部的地址解析器

总的来说要解决的就是用VHDL实现组件、地址解析器以及存储器控制器中的FIFO(FIFO主要是为了适配前后数据宽度的不同而设计)

总的来说要解决的就是用VHDL实现组件、地址解析器以及存储器控制器中的FIFO(FIFO主要是为了适配前后数据宽度的不同而设计)

基本概念解释:

1、容器:组件直接运行在容器之中,容器是组件实时的直接的运行环境,并为组件提供一些本地的/实时的服务和API(Application Programming Interface 应用编程接口),负责组件的本地调用、控制和管理。

2、组件:一个独立定义的应用或者波形的功能单元,它能够被独立的设计和部署,并且可以根据需要进行升级,是一个波形应用最基本的功能单元。根据所在的处理器的不同,存在多种实现方式。例如,同一个功能的组件,如果用DSP或者GPP实现,组件可以用C/C++语言开发;如果用FPGA实现,组件则用硬件描述语言开发。

3、Master和Slave是OCP接口

希望高手指点一二,再次感谢!

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。